-

[반도체-이론편] 1-2 반도체 산업개인 공부/반도체 2024. 11. 2. 00:05

반도체 밸류체인 (원재료 조달부터 완제품 최종 소비에 이르기까지 재화·서비스·정보 흐름이 이뤄지는 연결)

출처 : 삼성 반도체 이야기 - IDM(Integrated Device Manufacturer) : 설계, 제조, 패키징, 테스트까지 일괄 공정 체제를 구축한 완성 업체

- ex) 삼성전자, SK 하이닉스, 인텔, 마이크론, IBM, 온세미컨덕터 ...

- FAB-lite : 반도체 설계와 생산을 모두 수행하지만, 생산의 일부 또는 대부분을 외부 파운드리 업체에 맡기는 기업으로, IDM과 팹리스의 중간 형태이다.

- ex) 인텔, STMicro, Sony, NXP, Renesas, TI ...

- 칩리스 : 수요에 맞춰 블록 (IP, 지적 재산권)을 제공해주는 업체. 자신들의 설계대로 만들어진 칩이라 할지라도 칩에 대한 소유권을 가지지 않는다. 칩에 대한 IP를 제공해줌으로써 수익을 얻는다. 예전에는 팹리스가 각 블록을 모두 개발하였으나, 특화 설계의 필요성이 늘어나면서 칩리스가 블록 개발 외주를 맡고 있다.

- ex) ARM, 에이디테크놀로지 ...

- 팹리스 : 생산 설비가 없는, 칩의 설계를 전문으로 하는 업체. 칩리스 업체와 달리, 파운드리에 칩의 생산을 맡기고 생산된 칩에 대한 소유권을 가지고 판매한다.

- ex) NVIDIA, 구글, 애플, 퀄컴, 브로드컴, AMD ....

- 디자인 하우스 : 팹리스 업체가 제조한 설계 도면을 레이아웃으로 다시 디자인 하거나, 팹리스에서 제작한 레이아웃을 검증하는는 백엔드 디자인을 수행한다.

💡삼성전자 파운드리 사업부는 자체 가치사슬 프로그램(SAFE, Samsung Advanced Foundry Ecosystem)을 구동하는 노력을 하고 있다.- ex) GUC, 알파칩스 ...

- 파운드리 : 설계 전문 업체(팹리스)로 부터 주문받은 칩의 생산(전공정과정)을 전문적으로 하는 업체로, 실제로 물리적으로 반도체 제품을 구현한다. 파운드리 업체는 설계업체에게 자신의 기술수준이 담긴 PDK(Process Design Kit)를 제공하면서 자신들의 공정기술을 써서 제품을 만들어 달라고 마케팅한다.

Pure-Play 파운드리는 자체설계 없이 오직 수탁생산만 하며, IDM 파운드리는 자체설계 및 수탁생산을 병행한다. 주로 Pure-Play 파운드리 업체가 대부분을 차지하고 있다.

- ex) TSMC, UMC, Global Foundries, SK 하이닉스 시스템, 삼성전자, DB 하이텍 ...

- OSAT(Outsourced Semiconductor Assembly Test, 반도체 후공정) : 후 공정(패키징, 테스트)을 전문적으로 담당하는 업체

- 패키징은 칩과 외부를 연결하는 작업으로, 반도체 칩을 물리적으로 보호하고 상호 배선 및 전력 공급을 위해 필요한 공정이다. 반도체 칩이 예전에 비해 크기가 작아지고 고속동작을 수행함에따라 발열량이 높아지고 있기 때문에 패키징에서는 발생한 열을 바깥으로 잘 빼주는 방열 기능이 매우 중요해졌다.

- 테스트는 FAB공정이 끝난 "웨이퍼"를 대상으로 테스트 하는 웨이퍼 레벨 테스트와 / "패키지가 완료된 칩"을 검사하는 패키지 테스트로 구분된다.

💡삼성전자와 SK하이닉스는 자체적으로 첨단 패키징 기술을 개발해나가고 있다.

- ex) Amkor, ASE, ChipPAC, JOET, J-Devices, Power-tech, SPL ...

반도체 시장

- 반도체 제품 중 (개별소자, 광소자, 집적회로, 센서 등..) 80%이상은 집적회로 분야가 차지하고 있다.

- 집적회로 중 28%는 메모리 반도체가 차지하고 있다.

- 메모리 반도체 중 DRAM은 57.5%, 플래시 메모리는 42.5%를 차지한다.

- 집적회로 중 비메모리 반도체의 비중은 메모리 반도체의 2배 이상이다.

- 비메모리 반도체 중 AP, CPU, GPU 등으로 대표되는 로직 반도체의 규모가 가장 크며, 수요 또한 꾸준히 증가하는 추세이다.

- 아날로그 반도체는 로직 반도체와 달리 초미세 공정을 사용하면 도리어 소자의 성능이 열화되는 특성을 가지는 경우가 많다. => 아날로그 반도체는 성숙 공정의 수요와 공급이 꾸준히 지속되고 있다.

또한, 로직반도체와 달리 아날로그 반도체는 다품종 소량 생산도 필요하다. 이에 맞춰 12인치 뿐만 아니라 8인치 반도체 라인에서도 제작되괴 있다.

(💡 성숙공정, Legacy Node : 최신 미세 공정보다 상대적으로 큰 공정 노드에서 제조되는 반도체 공정으로, 일반적으로 28nm 이상의 공정을 말한다. 여기서 말하는 "성숙"이란, 이미 충분히 검증되고 안정화되어 있어 생산 과정에서 결함이 적고 수율이 높기 때문에 붙여진 이름이다. 최신 공정에 비해 장비와 생산 비용이 낮아 비용효율이 높다는 장점이 있다. 성숙 공정은 상대적으로 낮은 성능이나 전력 효율이 필요한 산업에 적합하다.)

- 집적회로 중 28%는 메모리 반도체가 차지하고 있다.

- 직접회로이외의 개별 소자, 광학 소자, 센서또한 상당한 규모를 차지하고 있다.

- 개별 소자는 주로 전력 반도체가 차지하고 있다.

- 실리콘 외에도 질화갈륨(GaN)이나 실리콘카바이드(SiC)등 차세대 반도체 소재를 이용한 제품이 존재한다.

- 질화갈륨은 내압 특성이 우수하고 스위칭 속도가 빨라 고주파, 고출력 환경의 무선통신용으로 적합하다.

- 실리콘카바이드는 내압특성이 우수하고, 안정성이 좋아 전기차 시장에서 수요가 증가하는 추세이다.

- 광학 소자(광전지, 레이저, LED ..) 중에서는 태양전지의 비중이 증가하는 추세이다.

- 센서 시장은 카메라 센서로 사용하는 CIS의 시장 규모가 증가하고 있다. 자율주행을 위해 라이다, 레이더 등과 함께 카메라 센서의 사용이 기하급수적으로 늘어나고 있다.

(💡LiDAR : 레이저 빛 즉, 빛의 전달 시간을 기반으로 거리 파악. 레이저는 거리에 따라 강도가 약해지므로 측정거리가 짧으며, 3D 맵을 위해 주로 사용된다.

Radar : 라디오파 기반으로 거리 파악. 안개,어두운 환경에서도 가능하며 측정거리가 길지만 정밀도는 낮다. 위치탐지나 차량 주행보조 시스템(ADAS)에 주로 사용된다.)

최근 반도체 산업 트렌드

끊임 없는 인수 합병

- SK하이닉스의 인수

- intel 낸드 플래시 사업부 인수

: SK하이닉스는 메모리 반도체 분야에서 D램에 비해 상대적으로 약했던 낸드 플래시 부문의 경쟁력을 강화하기 위해 2020년 10월 인텔의 낸드 플래시 사업부를 약 10조 3,104억 원에 인수하기로 결정했다. SK하이닉스는 이미 낸드 플래시 메모리 사업을 하고 있었지만, 인텔의 낸드 플래시 사업부를 인수함으로써 이 분야에서 경쟁력을 더욱 강화해 나갔고, 그 결과 SK하이닉스는 낸드 플래시 시장에서 글로벌 2위로 도약하며, D램에 편중된 사업 구조를 개선하고 메모리 반도체 분야에서의 경쟁력을 강화하게 되었다.

(💡인텔은 IDM회사로, 주로 CPU와 데이터 센터용 프로세서에 강점을 가진 기업이다. 인텔은 주력 사업인 CPU와 데이터 센터, AI, 자율주행 분야에 더 많은 자원을 집중하기 위해, 비핵심 사업인 낸드 플래시 부문을 정리하기로 결정하고 SK 하이닉스에게 넘겼다.) - 키파운드리 인수

: SK하이닉스는 파운드리(반도체 위탁 생산) 사업을 확대하기 위해 2021년 10월 국내 8인치 파운드리 기업인 키파운드리의 지분 100%를 약 5,758억 원에 인수하기로 결정했다. 그 결과 SK하이닉스는 파운드리 생산 능력을 두 배로 확대하여 비메모리 반도체 분야에서의 경쟁력을 강화하고자 하였다. 8인치 웨이퍼는 상대적으로 저렴하고, 전력 관리 반도체(PMIC), 디스플레이 드라이버 IC(DDI), 아날로그 반도체 등 기술적으로 고도화된 공정이 필요 없는 비메모리 반도체에 적합한 제품이다. 이러한 이유로 SK하이닉스는 최신 기술 공정이 필요 없는 비메모리 반도체 생산에 8인치 파운드리를 활용하면서, 효율적인 비용과 안정적인 수익을 확보하고자 키파운드리를 인수하였다.

- intel 낸드 플래시 사업부 인수

기술력 강화 경쟁

- DRAM 처럼 10나노미터 이하 공정이 가능한 업체는 인텔, TSMC, 삼성전자 3개 회사밖에 없다.

- 한동안 인텔은 CPU,GPU와 같은 로직 반도체를 주도하는 선구자였으나, FinFET이라는 신구조 개발 후 마케팅에 치우치는 전략을 고수하다 기술 경쟁에서 잠시 뒤처지기도 하였다.

- TSMC, 삼성전자는 EUV 설비 도입, FinFET 구조 최적화와 GAA구조 신규 개발의 대결 등 경쟁이 더욱 심화되어 있다.

- 애플은 그간 스마트 디바이스 등에서만 자체 개발 SoC 칩을 사용하고, PC에는 인텔의 칩을 받아 사용했지만 최근에는 자체 개발 칩을 PC에 사용하고 있다.

- 구글, 마이크로소프트, 아마존 등 IT업종으로 평가받던 기업들도 자체 칩을 생산하려는 시도를 하고 있다.

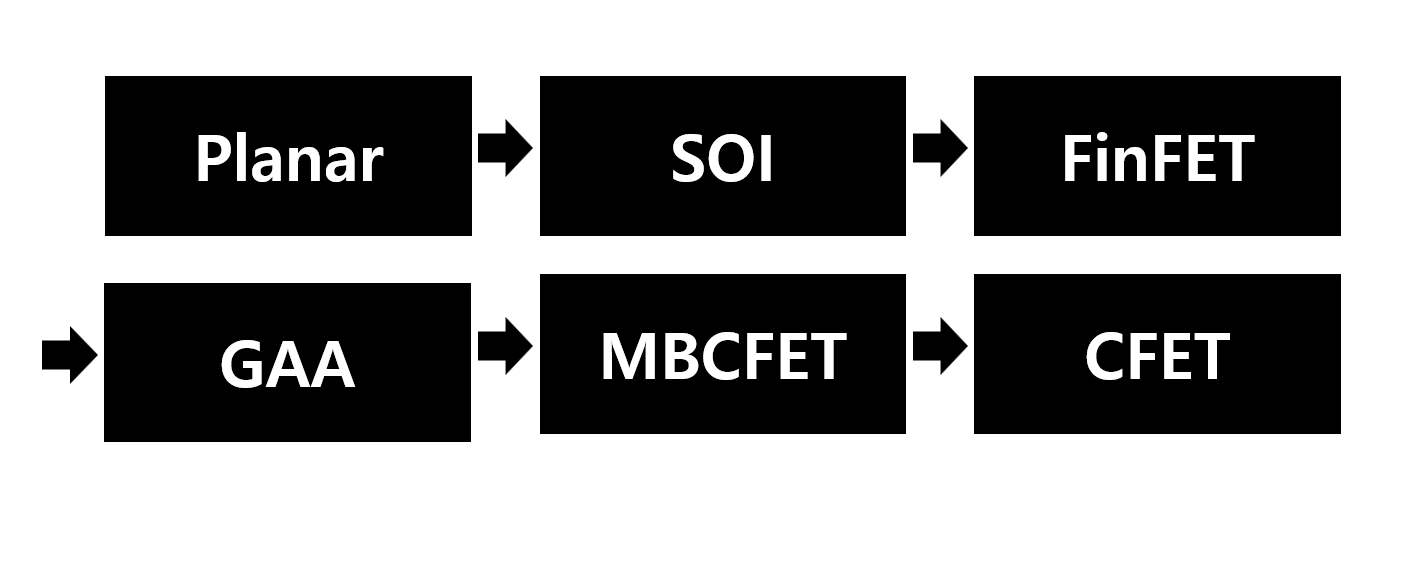

+💡MOSFET의 발전 과정

Planar

- 평면 구조

- 채널길이가 짧아짐에따라 채널 아래 기판에서 누설전류가 흐르는 문제가 더욱 심각해진다는 문제점이 있음

- 이 외에도 DIBL, Punch through와 같은 short channel effects 문제가 나타난다는 문제가 있음

=> 기판을 절연체(insulator) 같은 걸로 막아서 누설 전류를 차단하자는 개념에서 나온 것이 바로 SOI

SOI (Silicon On Insulator)

- 채널 아래를 절연채(insulator)로 막아 누설전류를 흐르지 못하게 함.

- 하지만, 다음의 이유 때문에 거의 사용되지 않음.

- SiO2와 같은 절연체로 body를 채우는 경우 그 위에 소스, 드레인을 위한 실리콘(=싱글 크리스탈)이 잘 자라지 않기 때문에 만들기 매우 까다롭고, 가격이 매우 비싸다는 단점이 있음

- Body 부분이 절연체로 이루어져 있기 때문에 어떤 영역과도 연결되지 못함 == 기판과 전기적으로 연결되지 못한 floating 상태이므로 floating body effect가 발생한다는 문제가 있음

(* floating body effect : body에 전자가 축적되어 전원이 꺼져있음에도 누설전류가 흐르거나 성능이 일관되지 않게 동작하는 문제점)

=> 이러한 문제를 해결하기 위해 3D 형태로 설계하여 gate를 채널 주위에 둔 것이 바로 FinFET

FinFET (= Double-gated MOSFET)

- 사진처럼, FinFET은 channel의 삼면을 gate가 둘러 싸고 있음을 알 수 있음

- 이때, 코너 부분에 전자가 많이 흐르는 corner effect 문제가 발생하기 때문에 이를 없애기 위해 채널 실리콘 위에 hard mask를 덮어버려 gate와의 접촉이 차단됨 => 따라서 "double-gated" MOSFET익라고 불림!

=> 그렇다면 gate를 channel의 사면에 모두 배치하면 더 좋지 않을까 해서 나온게 GAA

GAA (Gate All Around)

gate끼리 서로 이어져 있음- 위 사진 처럼 동그랗게 Nanowire형태로 만들면 corner effect를 없앨 수있으므로 가장 좋지만, 공정과정에 큰 어려움이 동반함

=> 동그란 모양에 가깝게 만들면 corner effect를 완전히 없앨 수 있음.

이러한 원리를 적용시켜 Nanosheet형태로 만든 MBCFET은 GAA의 구체적인 구현 형태 중 하나임!MBCFET (Multi Bridge Channel FET)

- 여러 개의 평평한 나노시트(nanosheet) 채널을 사용하는 구조

- 게이트가 얇고 긴 나노시트 형태의 채널을 감싸면서 전류를 제어한다.

=> 이왕 저렇게 여러개의 채널을 쌓을거면,

서로 다른 형태의 P형 및 N형 트랜지스터를 수직으로 쌓아 효율적인 CMOS를 만들자! 해서 나온 것이 바로 CFET

CFET (Complementary FET)

- CFET은 P형 및 N형 트랜지스터를 서로 위아래로 적층하여 공간 효율성을 극대화한 구조

- 해당 FET은 현재 연구 단계임

- Vss, Vdd의 간격이 너무 짧아 Vdd가 제대로 걸릴지에 대한 문제,

- 이종의 물질을 박아 넣었기 때문에 괜찮을지에 대한 문제 등은 고려해 봐야 할 문제..!

'개인 공부 > 반도체' 카테고리의 다른 글

[반도체 공학] 1. 고체의 결정 구조 (0) 2024.11.03 [반도체-이론편] 1-1 반도체 입문 (4) 2024.10.30 - IDM(Integrated Device Manufacturer) : 설계, 제조, 패키징, 테스트까지 일괄 공정 체제를 구축한 완성 업체