-

[digital] PLD 종류 (SPLD, CPLD)개인 공부/회로 2024. 12. 1. 03:17

PLD가 무엇인지 모르신다면,

아래 포스팅을 먼저 읽어보세요!😉

↓

https://ballbigdiary.tistory.com/45

[digital] PLD란?

PLD(Programmable Logic Device)AND array + OR array로 이루어진 IC각 게이트 입력에 퓨즈링크가 연결되어 있다.퓨즈 링크를 전자적으로 연결하거나 끊음으로써 원하는 동작을 하는 조합 논리 함수를 구현할

ballbigdiary.tistory.com

간단한 SPLD (Simple PLD)

- ROM, EPROM, EEPROM, PAL, PLA 등…

- 퓨즈(일정 값 이상의 전류가 흐르면 끊어지는 장치) 방식으로 연결되어 있어 재프로그래밍 불가능하다.

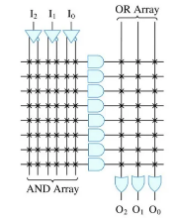

PLA

- PLA는 양쪽 다 프로그래밍 가능한 형태를 이루고 있다.

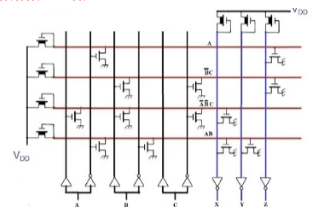

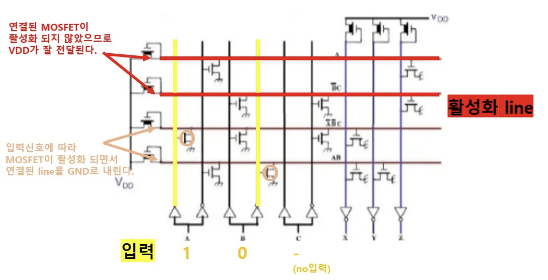

EX) 다음과 같이 설계된 PLA에 ABC = 10- 입력이 들어간 경우를 살펴보자

- 1. NAND array

위 회로도에서, 입력 A,B,C에 따라 선이 활성화 되면,

해당 선과 연결된 gate에 전압이 인가됨에 따라 MOSFET이 활성화 된다.

⇒ 해당 MOSFET에 연결된 line을 GND로 끌어 내려 비활성화 시킨다.

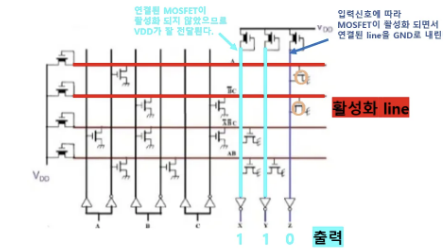

- OR array

빨간 line이 활성화 되면,

해당 line과 연결된 MOSFET이 활성화 된다.

⇒ 해당 MOSFET에 연결된 line을 GND로 끌어내려 0이 출력되게 한다.

⇒ 즉! 설계 목적에 맞게 MOSFET을 연결함으로써 원하는 논리 함수를 구현할 수 있다.

PROM

- 고정 AND array(decoder) + 프로그래머블 OR array 구조

- ROM은 비휘발성 메모리로, 주로 컴퓨터에 전원이 처음 공급될 때 컴퓨터를 기동시키기 위한 명령어(부트로더)를 저장하는 데 사용한다.

- 부트로더 말고, 임이의 논리함수를 구현하는 함수 생성기로서도 사용될 수 있다.

↓

출처 : https://insoobaik.tistory.com/m/649

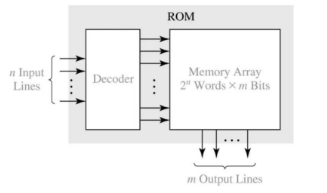

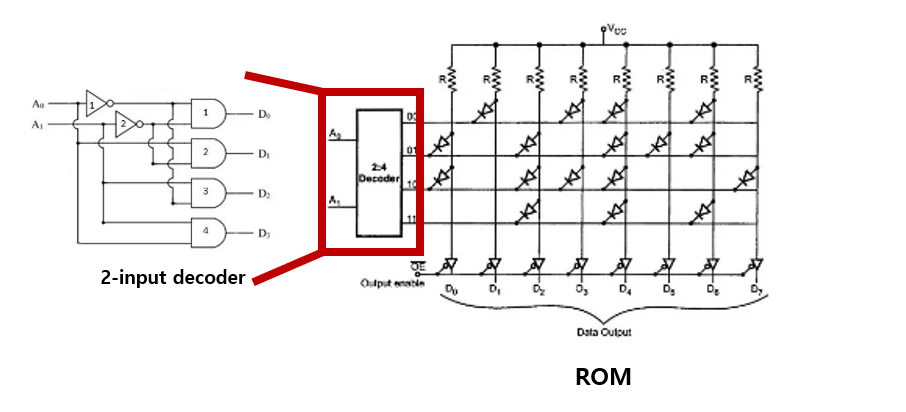

2bit input을 가지는 ROM의 전체 구조 - input : 디코더에 입력으로 들어간다.

- Decoder : 주어진 Nbit 입력에 대해 가능한 모든 minterm을 생성해준다.

- Diode : 수직-수평의 교차점에 위치하며, 전압이 인가된 수평선에 대해 output 입력을 차단해주는 역할을 한다.

- output : 입력에 각 조합에 대해 저장된 데이터가 출력된다.

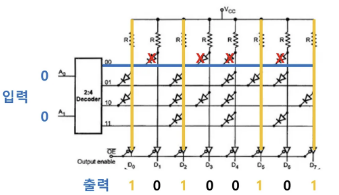

EX) 동작예시 : A0A1 = 00 입력

- 디코더 출력 = 1000 (decoder에 의해 D0만 활성)

- D0에 연결된 다이오드에 역방향 전압이 걸리면서 차단된다.

- 차단된 선은 0, 차단되지 않은 선은 1이 출력된다. ⇒ 최종 출력 = 10100101

- 즉, 입력 D0은 10100101 데이터를 저장하고 있다.

PAL

- 프로그래머블 AND array, 고정 OR array를 가진다.

- PLA보다 제조비용이 저렴하고, 집적도가 높다.

- 모든 minterm이 아닌, AND array를 프로그래밍 하여 원하는 minterm만 얻어낼 수 있다.

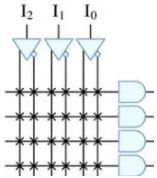

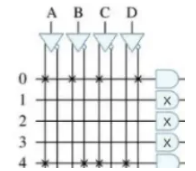

퓨즈맵

- 위 사진에서, X로 표시된 곳은 퓨즈가 연결되어 있음을 의미한다.

- 이때, 사용자는 목적에 맞게 특정 퓨즈를 끊어야 하는데, 이때 태워질 퓨즈의 위치를 열거하는 것이 퓨즈맵(JEDEC)이다.

- 1: 퓨즈가 연결됨(활성화).

- 0: 퓨즈가 끊어짐(비활성화).

ex) 퓨즈맵 예시

STX; (파일 시작) QF40; (총 퓨즈 수: 5행 × 8입력 = 40개) F0*10101001; (0번 행의 퓨즈 상태) F1*00000000; (1번 행의 퓨즈 상태) F2*00000000; (2번 행의 퓨즈 상태) F3*00000000; (3번 행의 퓨즈 상태) F4*10011010; (4번 행의 퓨즈 상태) C0143; (체크섬 값, 예제 값) ETX; (파일 끝)💡체크섬이란?

- 역할 : 데이터의 무결성을 검증하기 위해 사용되는 값

- 계산 방법 : 데이터의 비트 패턴을 일정한 알고리즘으로 계산하여 얻을 수 있다.

- 동작 원리 : 전송 받은 데이터에서 계산 방법에 맞게 체크섬을 계산하여 명시된 체크섬의 값과 비교하여 손상 여부를 판단한다.

- 한계 : 데이터의 손상 여부는 판단 가능하지만, 어떤 데이터가 손상 되었는지를 알 수 없으며, 데이터를 복구하거나 교정할 수도 없다.

[계산 과정]

1. 각 퓨즈행 F0~F4의 값을 모두 합산한다.

2. 합산한 값의 일부 하위 비트만 추출한다.

3. 추출한 비트를 16진수로 변환하여 체크섬 값을 얻는다.

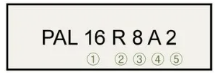

⇒ 전송 받은 체크섬 값과 계산된 체크섬 값이 서로 다르다면 데이터가 손상되었음을 의미한다!📌 PAL 읽는 방법

① : 입련 핀의 수

② : 기능 분류 기호 (R = 레지스터로 되어 있음을 의미)

③ : 출력이 있는 경우, 출력 핀의 수

④ : 지연시간의 버전. (지연 시간 : _ > A > B > D)

⑤ : 소비전력 형 (N = 1/N의 소비 전력을 의미)

GAL (Generic)

- PAL 구조는 모두 다름 (어떤건 레지스터가 있고, 어떤 건 입력이 적고, 어떤건 많고 등등…)

- GAL은 범용 목적의 PAL로서, 소규모의 인터페이스 논리를 구현하기 위한 최적의 device이다.

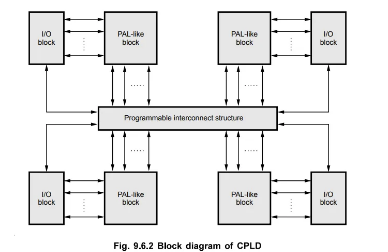

복잡한 CPLD (Complexed PLD)

- PAL 개념의 확장.

- SPLD = 단일 AND array + OR array를 가졌지만, CPLD = 그러한 SPLD 블록 여러개를 연결한 구조이다.

- 프로그램 가능한 행렬 구조 + PAL와 같은 로직 블록으로 구성된 IC

- CPLD는 논리 블록 간에 다양한 연결을 구성할 수 있어 더 복잡한 논리 회로도 처리 간능!

- 전기적으로 지울 수 있고, 재프로그래밍 할 수 있다.

구조

출처 : https://insoobaik.tistory.com/m/649 - Macrocell (매크로셀)

- CPLD의 기본 구성 요소로, SPLD의 기본 논리 블록(AND/OR 배열)을 포함

- 각 매크로셀은 논리 연산, 플립플롭, 상태 레지스터 등을 포함하여 조합 논리와 순차 논리를 처리

- Programmable Interconnect (프로그래머블 인터커넥트)

- 여러 Macrocell 및 I/O 핀 간의 연결을 설정

- EEPROM/플래시 메모리로 구성되어 있으며, 설계자가 정의한 논리 회로에 따라 선택적으로 매크로셀이 연결되게 해준다.

- 설계자가 원하는 대로 CPLD 내부의 SPLD 논리 블록들을 조합할 수 있는 유연성 제공함

'개인 공부 > 회로' 카테고리의 다른 글

[digital] 구조적 모델링 (0) 2024.12.19 [digital] 게이트수준 모델링 (1) 2024.12.19 [digital] Verilog HDL 모델링 (4) 2024.12.02 [digital] PLD란? (2) 2024.11.30