-

[digital] Verilog HDL 모델링개인 공부/회로 2024. 12. 2. 16:15

Verilog HDL 모델링

- Verilog HDL(하드웨어 기술 언어)에서 모델링 방식은 설계의 추상화 수준에 따라 나뉜다.

- 각각의 모델링 방식은 설계 목적, 복잡도, 그리고 시뮬레이션 요구사항에 따라 사용된다.

추상화 수준에 따른 분류

모델링 수준 설명 사용목적 추상화 수준 행위 수준 설계의 기능적 동작 정의 초기 설계 및 검증 높음 RTL 수준 데이터 경로와 레지스터 정의 합성을 위한 설계 중간 구조적 모델링 하위 모듈의 연결과 계층적 설계 계층적 설계, 재사용 가능 중간~낮음 게이트 수준 논리 게이트 단위의 동작 정의 합성 후 검증 낮음 트랜지스터 수준 트랜지스터 단위의 동작 정의 세부적인 회로 설계 가장 낮음

행위 수준 (고급 언어 프로그래밍과 유사)

- 실제 하드웨어가 아닌, 시스템의 기능적인 동작을 중점적으로 표현

- 테스트벤치 작성, 초기 설계 검증에 사용된다.

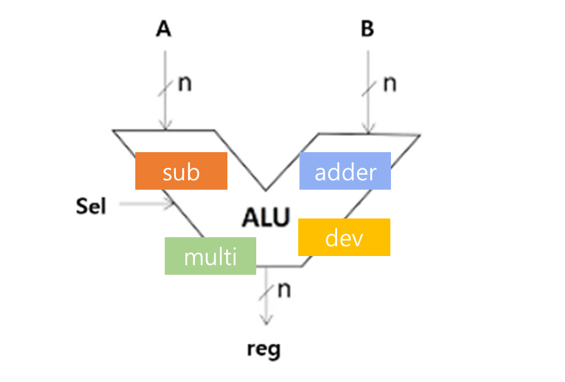

[행위 수준으로 작성된 ALU]

module alu(out, a, b, sel); output reg [7:0] out; input [7:0] a, b; input [2:0] sel; always @(a or b or sel) begin case (sel) 3'b000: out = a + b; 3'b001: out = a - b; 3'b010: out = a & b; 3'b011: out = a | b; default: out = 8'b00000000; endcase end endmodule

RTL 수준 (가장 많이 사용됨)

- 데이터의 흐름과 레지스터 간의 전송을 정의

- 설계가 하드웨어로 합성되기 전의 추상화 수준

[RTL 수준으로 작성된 4bit adder] => 행위 수준 : a+b = sum, cout

module adder ( input [3:0] a, // 입력 값 A (4비트) input [3:0] b, // 입력 값 B (4비트) input cin, // 입력 캐리 output [3:0] sum, // 출력 합계 (4비트) output cout // 출력 캐리 ); reg [4:0] temp; // 내부 계산용 (4비트 + 캐리) always @(*) begin temp = a + b + cin; // A와 B를 더하고 입력 캐리 추가 end assign sum = temp[3:0]; // 하위 4비트는 합계로 출력 assign cout = temp[4]; // 최상위 비트는 캐리로 출력 endmodule

구조적 모델링

- 하드웨어를 구성하는 하위 모듈을 연결하여 설계

- 상위모듈에서 하위 모듈을 인스턴스화하고, 각 모듈들을 연결하여 작성한다.

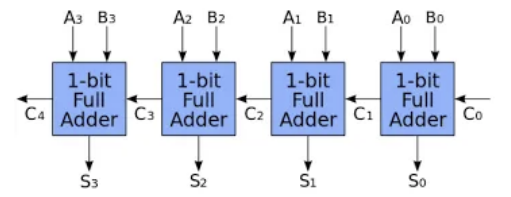

[구조적 모델링 방식으로 작성한 4bit Adder] => 1bit full_adder를 인스턴스화 하여 사용하여 구현

module ripple_carry_adder ( input [3:0] a, // 입력 A (4비트) input [3:0] b, // 입력 B (4비트) input cin, // 입력 캐리 output [3:0] sum, // 출력 합계 (4비트) output cout // 출력 캐리 ); wire c1, c2, c3; // 내부 캐리 신호 // **Full Adder를 인스턴스화하여 연결** full_adder fa0 (.a(a[0]), .b(b[0]), .cin(cin), .sum(sum[0]), .cout(c1)); full_adder fa1 (.a(a[1]), .b(b[1]), .cin(c1), .sum(sum[1]), .cout(c2)); full_adder fa2 (.a(a[2]), .b(b[2]), .cin(c2), .sum(sum[2]), .cout(c3)); full_adder fa3 (.a(a[3]), .b(b[3]), .cin(c3), .sum(sum[3]), .cout(cout)); endmodule

게이트 수준

- 논리 게이트(AND, OR, NOT 등)를 조합하여 설계

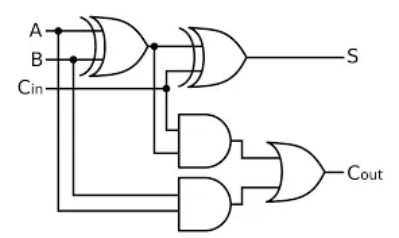

[게이트 수준으로 작성된 Full adder]

module full_adder ( input a, // 입력 A (1비트) input b, // 입력 B (1비트) input cin, // 입력 캐리 output sum, // 출력 합계 output cout // 출력 캐리 ); wire axb, axb_cin, ab; // 중간 신호 // 합계 (Sum) 계산 xor (axb, a, b); // axb = a ^ b xor (sum, axb, cin); // sum = (a ^ b) ^ cin // 캐리 (Carry) 계산 and (axb_cin, axb, cin); // axb_cin = (a ^ b) & cin and (ab, a, b); // ab = a & b or (cout, ab, axb_cin); // cout = (a & b) | ((a ^ b) & cin) endmodule

트랜지스터 수준

- MOSFET 또는 BJT 같은 실제 트랜지스터의 동작을 기반으로 모델링

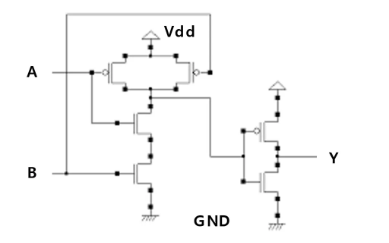

[트랜지스터 수준으로 작성된 AND게이트]

module and_gate ( input a, // 입력 A input b, // 입력 B output y // 출력 Y ); supply1 vdd; // VDD 전원 공급 supply0 gnd; // GND 접지 wire nand_out; // NAND 출력 // NAND 게이트 구현 (CMOS 방식) // Pull-Up Network (PMOS) pmos (nand_out, vdd, a); pmos (nand_out, vdd, b); // Pull-Down Network (NMOS) wire nmos_out; nmos (nmos_out, gnd, a); nmos (nand_out, nmos_out, b); // 인버터 구현 (NOT 게이트) // Pull-Up Network (PMOS) pmos (y, vdd, nand_out); // Pull-Down Network (NMOS) nmos (y, gnd, nand_out); endmodule'개인 공부 > 회로' 카테고리의 다른 글

[digital] 구조적 모델링 (0) 2024.12.19 [digital] 게이트수준 모델링 (1) 2024.12.19 [digital] PLD 종류 (SPLD, CPLD) (1) 2024.12.01 [digital] PLD란? (2) 2024.11.30